# **VeeCad Notes**

These notes cover how to use VeeCad with an EagleCad generated schematic. Veecad is a stripboard (strip board) / Veloboard editor which allows you to lay out such boards.

## Contents

| Create the Schematic $\underline{1}$ |

|--------------------------------------|

| Export Net List $\underline{1}$      |

| Import Net List <u>2</u>             |

| Defining New Components 4            |

| Select Board Size Z                  |

| Layout the Components. $\ldots $ 8 |

|------------------------------------|

| Building the Strip Board           |

| Test the Board <u>11</u>           |

## **Create the Schematic**

Create the schematic for your project in Eagle as usual. Once the schematic is done and passes ERC, you are ready to export the netlist to VeeCad.

# **Export Net List**

You are going to need the netlist\_protel User Language program for EagleCad. This is found here:

ftp://ftp.cadsoft.de/eagle/userfiles/ulp/netlist\_protel.ulp

Move this file to the Eagle ULP directory.

In the Eagle 'control panel', go to User Language Programs and you will find 'netlist\_protel.ulp':

| 🦳 net-bus-labeling.ulp    | NET/BUS labelingFor labeling nets automat    |

|---------------------------|----------------------------------------------|

| 🖳 📃 netlist-converter.ulp | Netlist converter for netlist from other CAE |

| - 📕 netlist_protel.ulp    |                                              |

| 🔤 nextdevdescript.ulp     | Edit next device description                 |

| 🛛 📒 nextpacdescript.ulp   | Edit next package description                |

| 🦳 🦰 normalize-text.ulp    | Normalize silkscreen text sizes              |

Right click and run in board (**don't use schematic** - it will cause import errors):

|   |     | netlist-co | nverter.ulp          |  |

|---|-----|------------|----------------------|--|

|   |     | netlist_pr | 0.000                |  |

|   |     | nextdev    | <u>O</u> pen         |  |

|   |     | nextpace   | <u>R</u> ename       |  |

|   |     | normalize  | <u>C</u> opy         |  |

|   |     | outlines.u | <u>D</u> elete       |  |

|   |     | panelize.ı | Duint                |  |

|   |     | part2htm   | Print                |  |

|   |     | pcb-serv   | Run in Schematic     |  |

|   |     | prevdevo   | Run in <u>B</u> oard |  |

|   |     | prevpace   | Run Ibrary           |  |

| 1 | JUP | nrint-indu | I SOUNT ENDING A     |  |

Now there will be a .net file:

| П       | extPtr.b#3<br>extPtr.brd<br>extPtr.net                 |

|---------|--------------------------------------------------------|

| u w 🖬 T | extP 5#1<br>extP Type: NET File<br>extP Type: NET File |

|         | extP<br>extP<br>Size: 1.21 KB                          |

# **Import Net List**

Start VeeCad, and click on Netlist | Import.

This will allow you to specify the .net file you just created. such as:

| Netlist Format                                                                                                                                                                                                                                                                                                    |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Protel                                                                                                                                                                                                                                                                                                            |   |

|                                                                                                                                                                                                                                                                                                                   |   |

| Netlist Filename                                                                                                                                                                                                                                                                                                  |   |

| C:\Documents and Settings\danh\Desktop\Eagle\TextPtr\TextPtr.net                                                                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                   |   |

| Libraries                                                                                                                                                                                                                                                                                                         |   |

| Libraries C:\Program Files\VeeCAD\library\V_Standard.per                                                                                                                                                                                                                                                          |   |

|                                                                                                                                                                                                                                                                                                                   |   |

| C:\Program Files\VeeCAD\library\V_Standard.per                                                                                                                                                                                                                                                                    | _ |

| C:\Program Files\VeeCAD\library\V_Standard.per<br>C:\Program Files\VeeCAD\Library\V_Alphabet.per                                                                                                                                                                                                                  |   |

| C:\Program Files\VeeCAD\library\V_Standard.per<br>C:\Program Files\VeeCAD\Library\V_Alphabet.per<br>C:\Program Files\VeeCAD\Library\V_Capacitors.per<br>C:\Program Files\VeeCAD\Library\V_Capacitors_Metric.per<br>C:\Program Files\VeeCAD\Library\V_Displays.per                                                 |   |

| C:\Program Files\VeeCAD\library\V_Standard.per<br>C:\Program Files\VeeCAD\Library\V_Alphabet.per<br>C:\Program Files\VeeCAD\Library\V_Capacitors.per<br>C:\Program Files\VeeCAD\Library\V_Capacitors_Metric.per<br>C:\Program Files\VeeCAD\Library\V_Displays.per<br>C:\Program Files\VeeCAD\Library\V_Relays.per |   |

| C:\Program Files\VeeCAD\library\V_Standard.per<br>C:\Program Files\VeeCAD\Library\V_Alphabet.per<br>C:\Program Files\VeeCAD\Library\V_Capacitors.per<br>C:\Program Files\VeeCAD\Library\V_Capacitors_Metric.per<br>C:\Program Files\VeeCAD\Library\V_Displays.per                                                 |   |

The standard libs appear to be useless because they don't work with Eagle; however, you can specify past projects. Here I specify my prior attempt at txtptr and it pulls out many of the last component outlines.

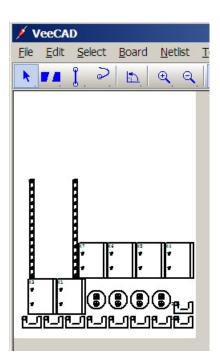

So I end up with this:

It did a decent job as I had already designed several of the components in the prior draft. All of the U shaped outlines still need to be defined.

Now go to Netlist | View | Validation. This should be clean or at least the errors make sense. If not, you will have to fix .net and import again.

Look at the Project View. Chances are there will be errors which are likely due to the component not yet being defined:

| 🕖 Ne | etlist |     |         |    |          |        |   |    |

|------|--------|-----|---------|----|----------|--------|---|----|

| Node | s Comp | one | nt Pins | Va | lidation | Projec | t |    |

| Net  | pin    | 1   | not     | on | Compo    | nent   | : | C2 |

| Net  | pin    | 2   | not     | on | Compos   | nent   | : | C2 |

| Net  | pin    | 1   | not     | on | Compos   | nent   | : | C5 |

|      | pin    |     |         |    | Compos   |        |   |    |

| Net  | pin    | 1   | not     | on | Compos   | nent   | : | C6 |

|      |        | -   |         |    | -        |        |   | _  |

# **Defining New Components**

Fortunately this is pretty easy. C2 is a small ceramic cap. We define an outline, then assign C2 to that outline. Note that the pins for C2 are 1 and 2. since this is not polarized, we don't have to worry about that yet.

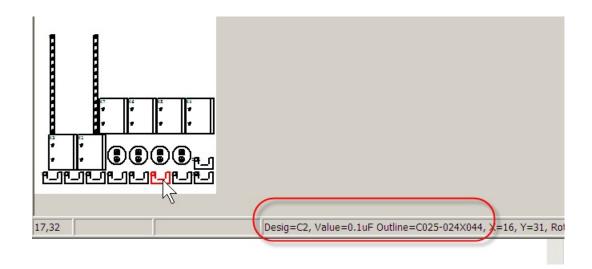

I find C2 and once selected I can see I have C2 and also see the outline name:

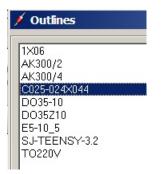

I need to define outlie C025-024.... . Now click on Board  $\mid$  Outlines and select that outline:

#### **Cell Outlines**

In the outline array right click to remove blocks and left click to add. My little capacitor is very simple and I label the pins 1 and 2:

| 1×06<br>AK300/2<br>AK300/4<br>C025-024×044<br>DO35-10 |               |

|-------------------------------------------------------|---------------|

| DO35Z10<br>E5-10_5<br>SJ-TEENSY-3.2<br>TO220V         |               |

|                                                       |               |

|                                                       |               |

|                                                       | 2 2<br>3<br>4 |

| New Rename Delete                                     | 3             |

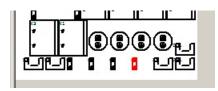

click on OK and now all capacitors using that outline have been corrected:

and now if you Netlist | View | Project, those caps are clean.

#### Leaded Outlines

D1 is going to be a leaded outline setup like this:

| 🗡 Outlines                                                                                             |                       |

|--------------------------------------------------------------------------------------------------------|-----------------------|

| 1×06<br>AK300/2<br>AK300/4<br>C025-024×044<br>DO35-10<br>DO35210<br>E5-10_5<br>SJ-TEENSY-3.2<br>TO220V | ↓<br>TveLeadedOutline |

|                                                                                                        | Body Length 2         |

| New Rename Delete                                                                                      | Body Width 1          |

| Celled Celled                                                                                          | Show Reference        |

| C Radial C Custom                                                                                      | Reference Pin Name C  |

| - 🔽 No Import                                                                                          | Pin Name A            |

#### **Custom Outlines**

Although the AK300/2 (a terminal block) outline imported from my TextPtr library, it is a good example of a custom component. Here is the basic definition:

| 🗡 Outlines                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AK300/2<br>BuckCvtr<br>C025-024044<br>D035-10<br>D035210<br>E5-10_5<br>SIM800L<br>S.J-TEENSY-3.2<br>T0220V | •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       • <t< th=""></t<> |

| New Bename Delete                                                                                          | Edit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Click on the edit button and you will see:

|   | Outline Editor |     |  |

|---|----------------|-----|--|

|   | ▼    ବ୍ ବ୍     | 8 8 |  |

|   |                |     |  |

| ▽ |                |     |  |

|   |                |     |  |

| ▽ |                |     |  |

|   |                |     |  |

|   |                |     |  |

|   |                |     |  |

|   |                |     |  |

Here you use the line tool to create lines, and the triangle tool to create pins and assign them names. The process is pretty quick and easy.

Continue until all components are defined (no U shaped components):

## **Select Board Size**

Now select the appropriate board size. Don't forget to verify the board is going to fit. Changing the size after the fact can be nasty.

| ile <u>E</u> dit <u>S</u> | elect <u>B</u> oard | <u>N</u> etlist <u>T</u> e | ools <u>H</u> el    | D        |   |               |       |

|---------------------------|---------------------|----------------------------|---------------------|----------|---|---------------|-------|

|                           | 2                   | Q Q                        | <b>\</b> • <u>=</u> | R2 / 3K/ | Ø |               |       |

| <br><b>1 1</b>            |                     |                            |                     |          |   | <br>          |       |

| N                         |                     |                            |                     |          |   | <br>          | <br>- |

| 1 🧮                       | he h                |                            |                     |          |   | <br>          |       |

|                           |                     |                            |                     |          |   | <br>          | <br>  |

|                           | TE T                |                            |                     |          |   | <br>          | <br>  |

|                           |                     |                            |                     |          |   | <br>          | <br>  |

|                           | · · · · · · ·       | THE REPORT OF THE          |                     |          |   | <br>          |       |

|                           | · · · · · · ·       | 1.1.1.1.1.1.               |                     |          |   | <br>1.1.1.1.1 |       |

| 1 · · · · · · ·           |                     |                            |                     |          |   |               |       |

|                           | 67 I KG             | 69 64                      |                     |          |   | <br>          | <br>- |

|                           |                     | · · · ·                    |                     |          |   | <br>          |       |

| 1 · · · · · · ·           |                     |                            |                     |          |   | <br>          | <br>- |

|                           |                     |                            |                     |          |   | <br>          | <br>  |

|                           |                     |                            |                     |          |   | <br>          | <br>  |

| 2 01                      |                     |                            |                     |          |   | <br>          |       |

|                           |                     |                            | · · · ·             |          |   |               |       |

|                           | III 🖉 Y 📕 Y 🖉       | <b>N N N</b>               |                     |          |   |               |       |

|                           |                     |                            |                     |          |   | <br>          |       |

| $\sim$                    |                     | · · · · · ·                |                     |          |   | <br>          |       |

|                           |                     |                            |                     |          |   | <br>          | <br>  |

# Layout the Components

You are ready to go!

Don't forget ALT-DRAG lengthens wires and leaded components

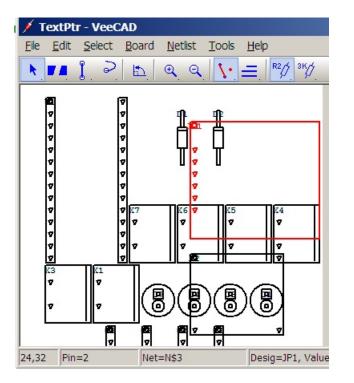

Once the board is layed out it will look something like this:

| C                        |

|--------------------------|

| 9 Power in Printer Power |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

| 10pBp1 10pCF JEE         |

|                          |

|                          |

|                          |

|                          |

|                          |

|                          |

# **Building the Strip Board**

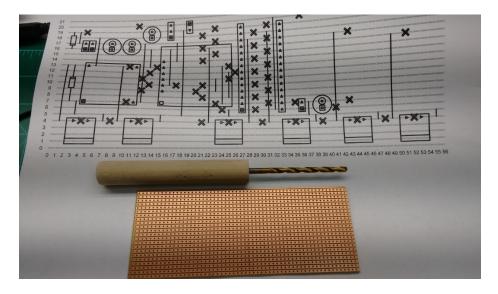

Once I'm ready to build the board, I print the front diagram (shown) and the back. You will need to use the back to layout the holes.

I built my trace cutter using

http://www.instructables.com/id/Stripboard-track-cutter/

Then the PCB is cut to the necessary size.

#### **Cutting Traces**

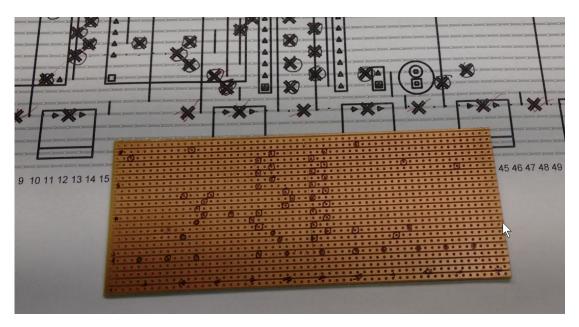

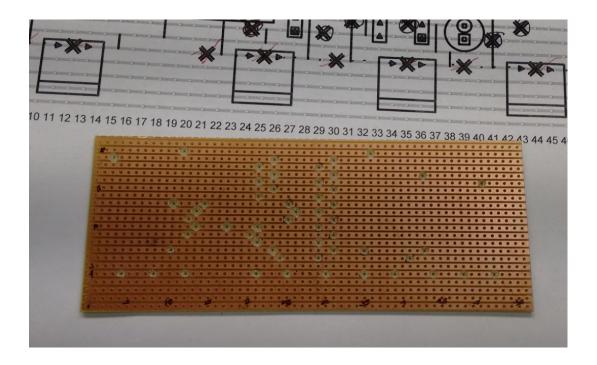

Next the X's are laid out on the board. I numbered the board by 5's to match the document. I then used the edge of 2 sheets of paper to work my way up the board row by row, marking each hole:

Now using the special tool, cut out all of the circles:

Installing and Soldering Components

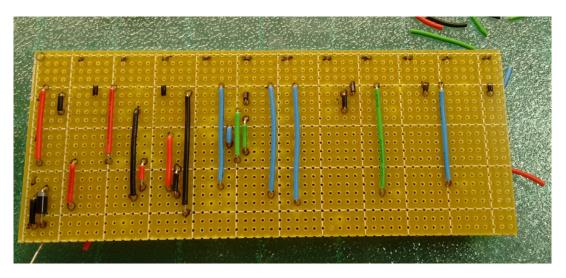

As with other boards, you want to start w/ the lowest profile components and work your way up. So I started with the jumper wires:

I then worked my way thru all the components:

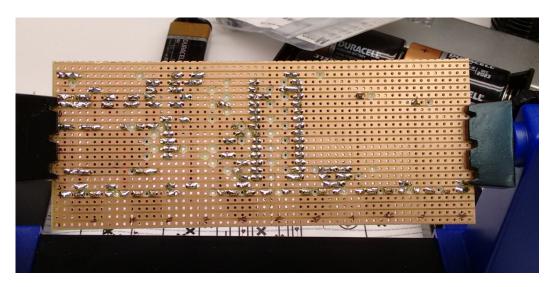

here is the bottom. Not pretty, but not the worst solder job I've done:

All of the cheap components were soldered in. The more expensive stuff is socketed.

## **Test the Board**

Next I test the board to verify voltages are where they should be, especially on MCU and other socketed chips.

Once I believe everything is in order, I insert the socketed chips and proceed with final testing.